## 2003 International Conference Characterization & Metrology for ULSI Technology

# CMOS Devices and Beyond A Process Integration Perspective

Jim Hutchby<sup>1</sup>, Victor Zhirnov<sup>1,2</sup>, Ralph Cavin<sup>1</sup>, George Bourinanoff<sup>3</sup>

- <sup>1</sup> Semiconductor Research Corporation

- <sup>2</sup> Materials Science & Engineering Dept., North Carolina State University

- <sup>3</sup> Intel Corporation and SRC

March 25, 2003

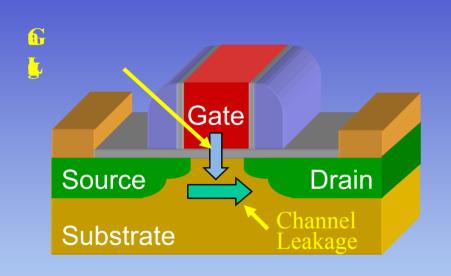

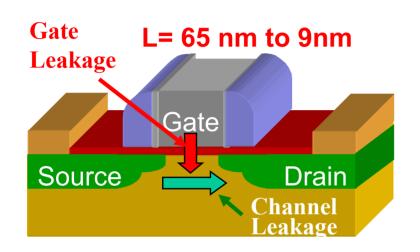

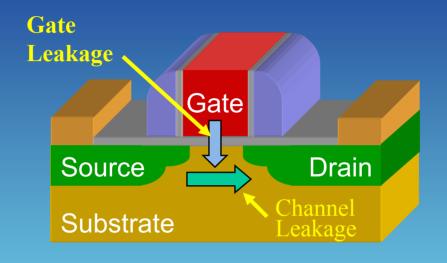

# Conventional Bulk-Si MOSFET Scaling Issues

#### **Primary barriers to MOSFET scaling are:**

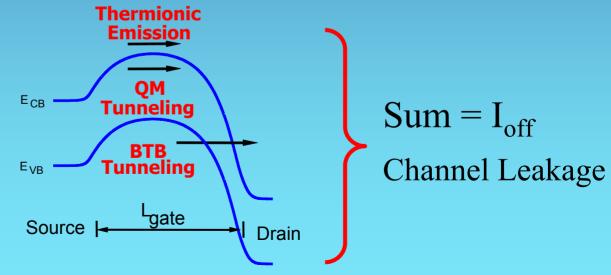

- High I<sub>on</sub>/I<sub>off</sub> ratio (I<sub>off</sub> = Channel leakage current)

- Low Standby leakage current (Gate + Channel leakage)

- Low channel leakage current (Electrostatic scaling)

- Low gate leakage current

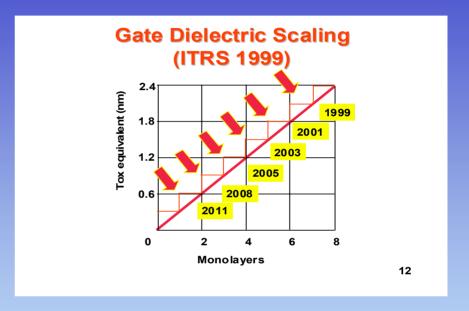

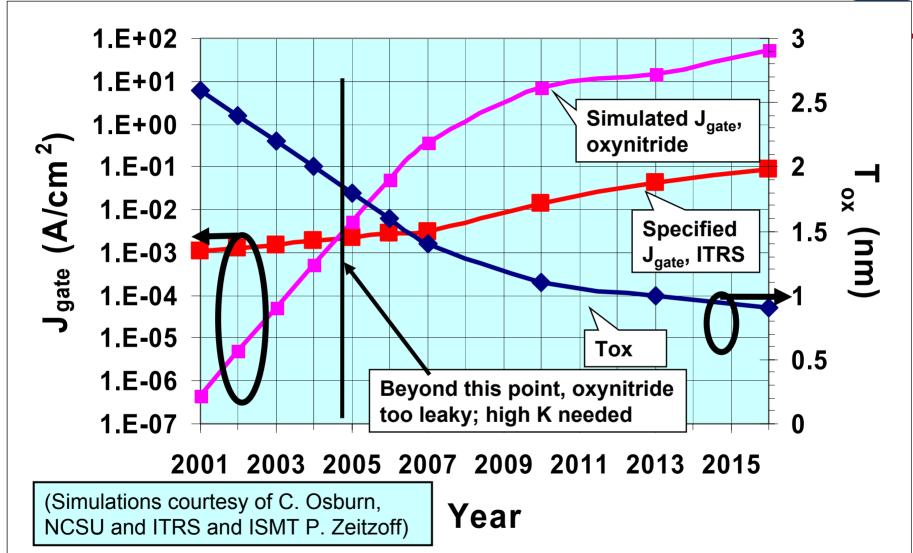

## 2001 ITRS Projections Vs. Simulations of Direct Tunneling Gate Leakage Current Density for *Low Power Logic*

Implementation of high-k will be driven by Low Power Logic in 2005

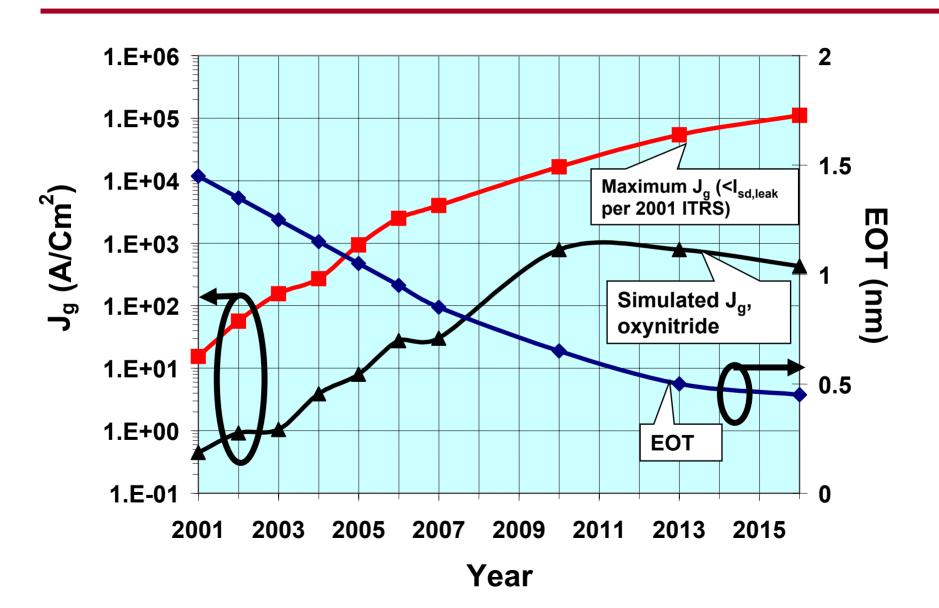

## 2001 ITRS Projections Versus Simulations of Gate Leakage Current Density for *High-Performance Logic*

# **CMOS Devices and Beyond Outline**

#### CMOS Devices ...

- MOSFET Scaling Issues

- Non-Classical CMOS Structures

- Ultra-Thin Body MOSFETs

- Channel Engineered Structures

- FinFETs

- Double Gate Structures

### And Beyond - Novel FET Structures and/or New Information Processing Architectures

- Potential of Molecular, Nanowire and Nanotube Electronics

- MOSFET-like switches?

- New Information Processing Technology?

- Limits on Integration Density Device Size or Power?

#### Conclusions

## 2003 International Conference Characterization & Metrology for ULSI Technology

# **CMOS Devices ....**A Process Integration Perspective

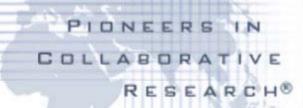

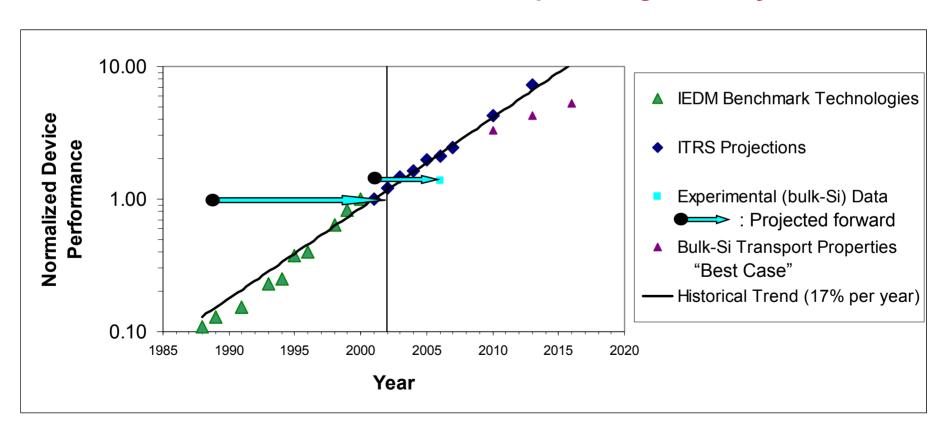

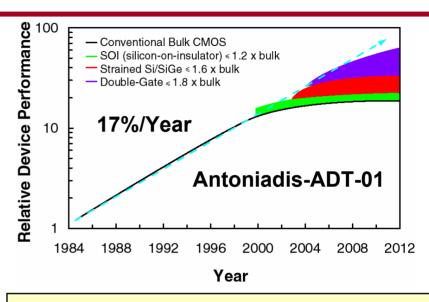

#### **Bulk-Si Performance Trends**

Maintaining historical CMOS performance trend requires new semiconductor materials and structures by 2008-2010... Earlier if current bulk-Si data do not improve significantly.

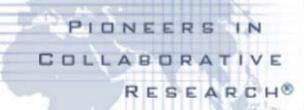

## New Materials & Non-Classical Structures for CMOS

## Nano-FET Scaling Fundamental Issues

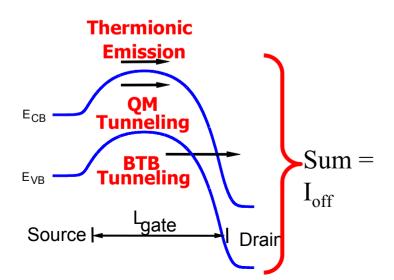

## Electrostatic and quantum scaling (I<sub>on</sub>/I<sub>off</sub>)

- Increase carrier transport and ballistic efficiency.

- Reduce quantum tunneling of electrons and holes.

- Break the tyranny of the universal mobility curve.

- Bandgap engineeredFET

New device architecture

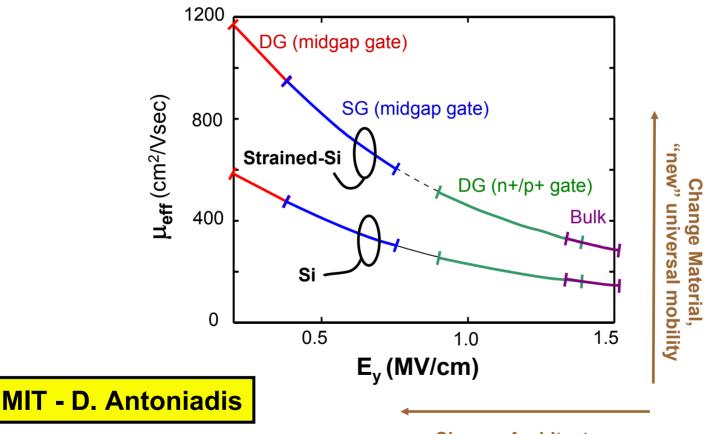

## Breaking the tyranny of the universal mobility: Alternative device structures & new Si-based materials

#### E<sub>v</sub> for constant inversion charge range for four device architectures

Change Architecture, "bulk-Si" universal mobility but reduced doping

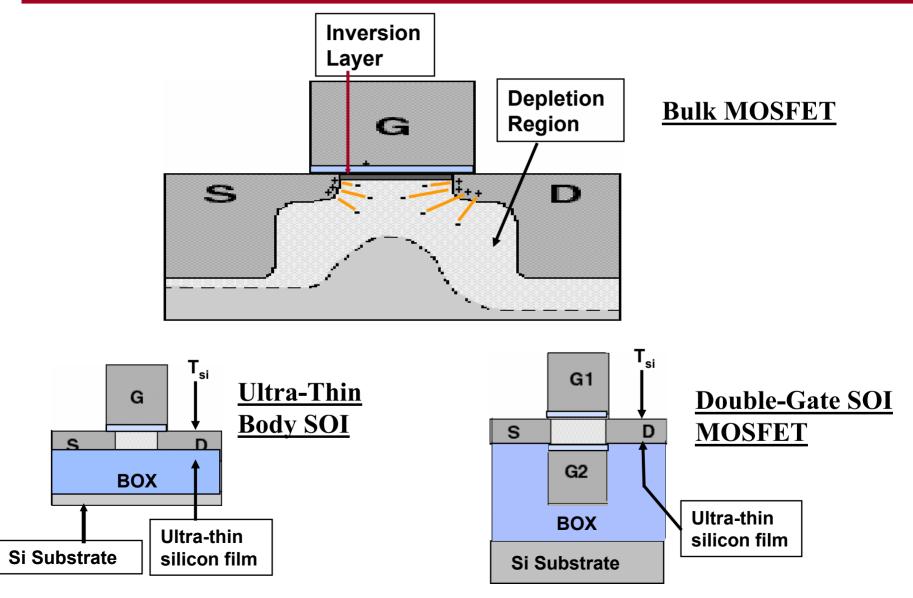

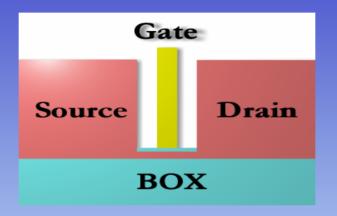

# Schematic cross section of planar bulk, UTB SOI, and DG SOI MOSFET

## **Ultra-Thin-Body MOSFET**

#### **Advantages**

- Suppresses channel leakage

- Improves V<sub>t</sub> controllability

- Raised Si/Ge source/drain improves I<sub>on</sub>

#### **Challenges**

- Requires ultra thin silicon channel

- Gate Stack

- Device characterization

- Compact model parameter extraction

## **UTB SOI MOSFET Scaling**

- Issues for bulk-Si MOSFET scaling obviated

- Body does not need to be heavily doped

- T<sub>ox</sub> does not need to be scaled as aggressively

EOT can be 5% lower for same I<sub>gate</sub> however (L. Chang et al., IEDM 2001)

- Ultra-shallow S/D junction formation is not an issue

- ◆ Body thickness must be less than ~1/3 x L<sub>gate</sub>

Scale length

$$l = \sqrt{T_{ox}} d \varepsilon_{si} / \varepsilon_{ox} + d^2 / 2$$

where  $d = T_{si}$

Formation of uniformly thin body is primary challenge

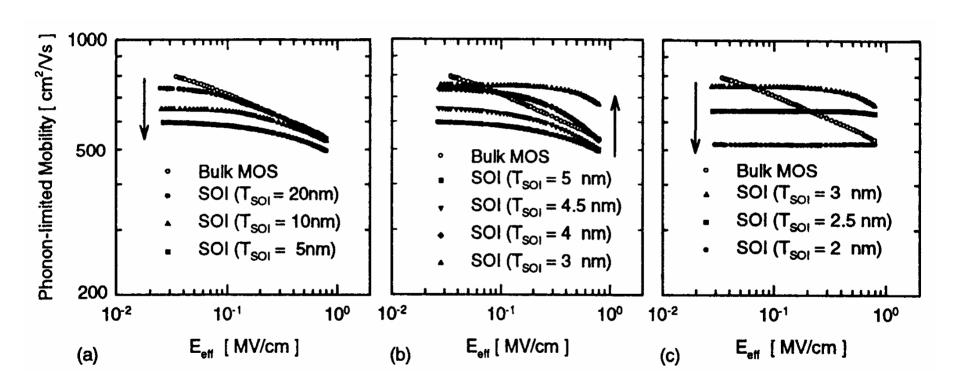

Theoretical mobility as function of silicon film. At Tsoi = 3 - 5 nm, mobility becomes higher than that in bulk Si MOSFET.

(S.Takagi et al.; SSDM '97, p.154)

# Advanced Gate Stack Materials for Thin-Body SOI MOSFETs

- High-κ gate dielectrics

- Desirable for reducing  $T_{ox,eq}$  to

- improve I<sub>dsat</sub>

- reduce short-channel effects

- Metal gate materials

Desirable to

- eliminate gate depletion effect

- reduce gate-line resistance

Necessary to achieve proper  $V_t$  in UTB MOSFETs (due to low body doping  $N_{body}$ )

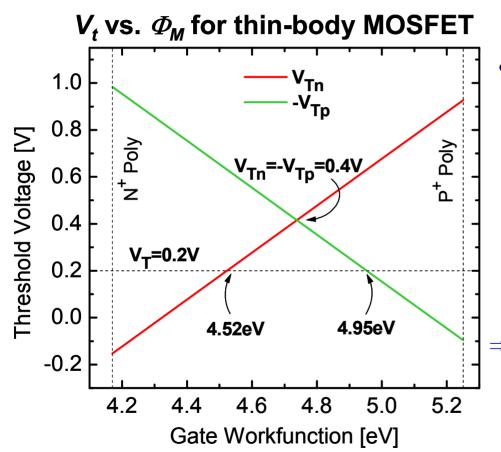

## Thin-Body MOSFET V<sub>t</sub> Control

**Gate Work-Function Engineering**

L. Chang et al., IEDM Technical Digest, pp. 719-722, 2000

- Low and symmetrical V<sub>t</sub>'s are desirable

- dual N<sup>+</sup>/P<sup>+</sup> poly-Si  $\Rightarrow V_{tn} = -V_{tp} = -0.1V \leftarrow too low$

- mid-gap gate material  $\Rightarrow V_{tn} = -V_{tp} = 0.4V \leftarrow too \ high$

- Need dual-work-function metal gates w/ tunable  $\Phi_{\rm M}$

~4.5V for NMOS; ~4.9V for PMOS

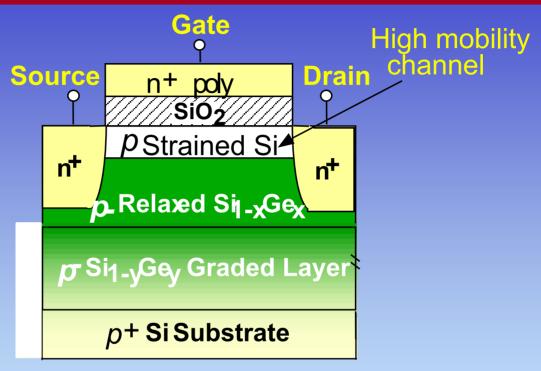

## **Band Engineered Transistor**

#### **Advantages**

- Higher drive current (I<sub>on</sub>)

- Compatible with bulk and SOI CMOS

MIT - J. Hoyt

#### **Challenges**

- High mobility channel film thickness for SOI

- Gate stack

- Integration process

- Device characterization

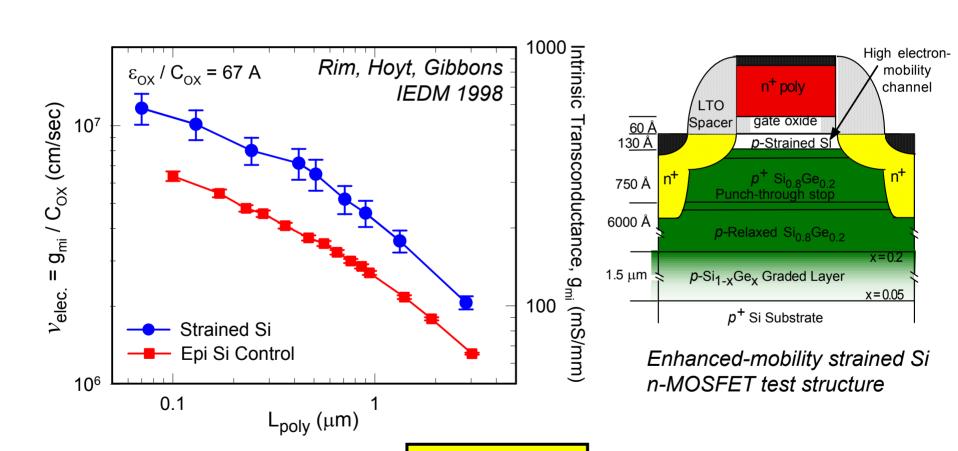

## Mobility Enhancement in Strained-Si-Channel n-MOSFETs

MIT - J. Hoyt

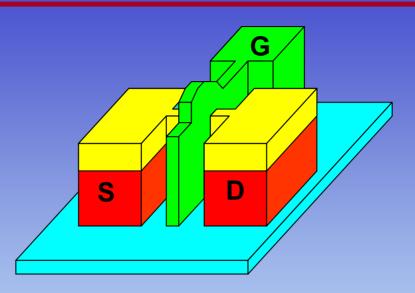

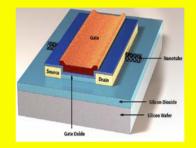

### **FinFET Structure**

#### **Advantages**

- Higher drive current (I<sub>on</sub>)

- Improved subthreshold

V<sub>t</sub> slope

- Improved short channel effect (electrostatics)

- Stacked NAND gate

#### **Challenges**

- Silicon film thickness

- Gate stack

- Process complexity

- Gate width available in integral steps

- Accurate TCAD

## FinFET Scaling

#### Compared with UTB-MOSFET:

- Reduced short-channel effects => more scalable

- Higher current drive due to

- steeper subthreshold swing (60 mV/dec)

- lower channel electric field => higher carrier mobilities

- Fin width must be less than  $2/3 \times L_{gate}$

Scale length

$$l = \sqrt{T_{ox} d \varepsilon_{si}/\varepsilon_{ox} + d^2/2}$$

where  $d = 0.5 x T_{si}$

Formation of narrow fin is primary challenge

sub-lithographic process needed

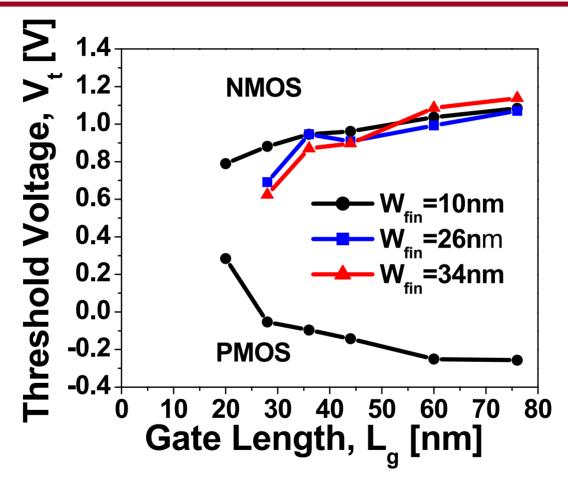

### FinFET V<sub>t</sub> Roll-Off Characteristics

Narrow W<sub>fin</sub> shows less V<sub>t</sub> roll-off.

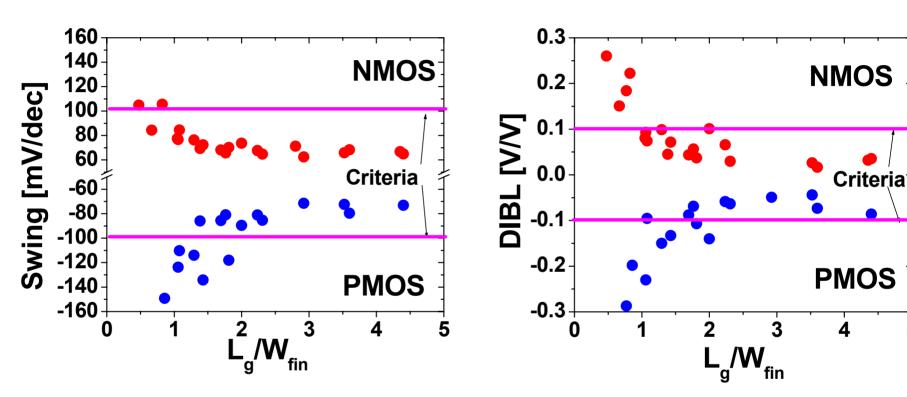

### Subthreshold Swing and DIBL

When  $L_g/W_{fin} > 1.5$ , S < 100mV/dec and DIBL < 0.1V/V.

## Performance of Intel's Tri-Gate p - and n - MOSFETs (Similar to the FinFET)

| Company | Channel<br>Length<br>(nm) | n- or p-<br>Channel | Subthreshold<br>Slope<br>(mV/dec) | DIBL<br>(mV/V) | Ion<br>(mA/um) | Ioff<br>(nA/um) | Vcc<br>(V) |

|---------|---------------------------|---------------------|-----------------------------------|----------------|----------------|-----------------|------------|

| Intel   | 60                        | n-MOS               | 75                                | 45             | 1.18           | 60              | 1.3        |

| Intel   | 60                        | p-MOS               | 70                                | 40             | -0.65          | -9              | -1.3       |

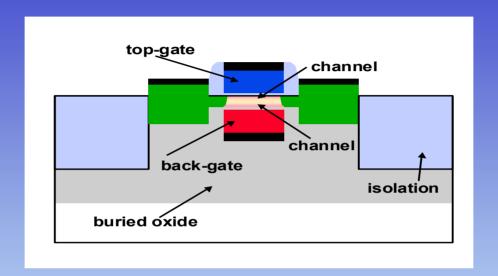

### **Double Gate Transistor**

#### **Advantages**

- Higher drive current (I<sub>on</sub>)

- Improved subthreshold V<sub>t</sub> slope

- Improved short channel effect (electrostatics)

- Stacked NAND gate

#### **Challenges**

- Gate alignment

- Silicon film thickness

- Gate stack

- Process complexity

- Accurate TCAD

### **Technology Scaling & Challenges**

- High-κ gate dielectrics not necessary to control short-channel effects, but will be helpful for achieving high I<sub>dsat</sub> (High-κ gate dielectrics will be necessary for low standby power applications)

- ◆ Parasitic resistance will be an issue for T<sub>Si</sub> < 10nm</p>

- Raised S/D technology but C<sub>overlap</sub> cannot be too high

- Schottky S/D technology eventually needed

- Metal gate electrodes (different from those used for classical MOSFETs) will be needed

- ❖ Multiple-V<sub>t</sub> technology will require tunable metal gate Φ<sub>M</sub>

- Structures which are provide for dynamic control of V<sub>t</sub> are desired by circuit designers

- Strained Si (for enhanced mobility) will be difficult to achieve

## **2003 International Conference**Characterization & Metrology for ULSI Technology

## .... and Beyond

# Fundamental Limits to Scaling Nanoelectronic Switch Elements

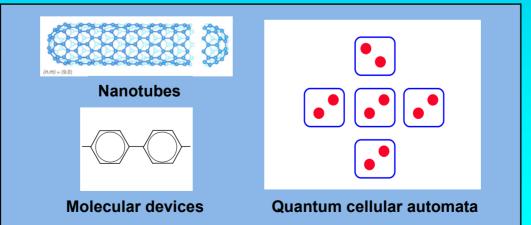

### **Scope of Emerging Research Devices**

## Ideal von Neumann's Computer

Highest possible integration density

Highest possible speed

Lowest possible energy consumption

### **Two Questions**

- 1. What is the best direction to pursue for alternate information processing technologies (e.g., carbon nanotubes, molecular electronics, etc.)?

- Replicate CMOS technology with new switches, gates, etc., directly one for one sustaining the von Neumann architecture? Or

- Eventually invent and develop a completely new information processing technology and systems architecture?

- 2. What is the best application of CMOS *gate or switch replacement* technologies, e.g., carbon nanotube switches or molecular switches?

- A completely new technology embodying not only the switch, but also the interconnect, I/O, etc. (completely replace CMOS) Or

- Use of the CNT or molecular switch to replace the channel of a silicon MOSFET, thus extending the silicon MOSFET infrastructure process technology for a longer time?

## Field Effect Transistor Electronic Switch 1330

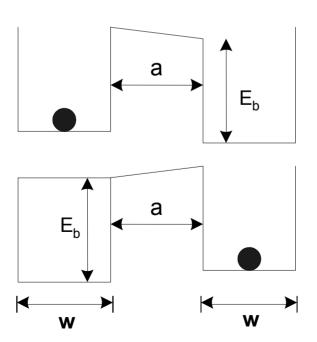

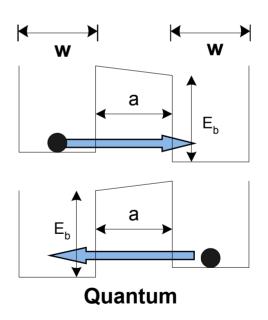

# Lowest Barrier: Distinguishability Barrier

Distinguishability D implies low probability  $\Pi$  of spontaneous transitions between two wells (error probability)

$$D=max, \Pi=0$$

$D=0, \Pi=0.5 (50\%)$

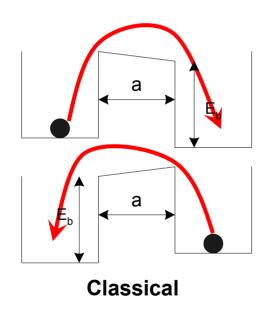

# Classic and Quantum Distinguishability

## **Limit Performance of Charge Based Switch**

**Minimum Barrier Width**

$$a_{crit} = 0.6 nm$$

Minimum Switch Width

**Maximum Gate Density**

$$n = 1 \times 10^{14} \frac{gate}{cm^2}$$

Minimum state switching time

$$t_{sc} = 2.3 \times 10^{-14} s$$

Total Power Consumption

$$P_{chip} = 2.0 \times 10^7 \frac{W}{cm^2}$$

## Comparisons with 2001 ITRS (2016)

Gate density

This analysis

$n = 1.0 \times 10^{14} \text{ gates/cm}^2$

\* ITRS

$n = 1.4 \times 10^9 \text{ gates/cm}^2$

Switching time

This analysis

t = 23

fs

\* ITRS

t = 150

fs (CV/I)

Power density

This analysis

$P = 2.0 \times 10^7 \text{ W/cm}^2$

**ITRS**

P = 93

W/cm<sup>2</sup>

Power density normalized to density and switching time

This analysis

P = 43

W/cm<sup>2</sup>

ITRS

P = 93

W/cm<sup>2</sup>

## Comparisons with 2001 ITRS (2016)

#### **Observations**

- ◆ Transistor critical dimension limited to ~ 1 nm (In the 2001 ITRS physical gate length = 9 nm for 2016)

- Power density, not critical dimension, limits gate density to  $\sim 1 \times 10^9$  gates/cm<sup>2</sup>

- For the ITRS density and switching time, CMOS is approaching the maximum power efficiency

#### A Point of View - - -

#### Are the most attractive directions for research?

#### Near term

Exploration of materials and structures for integration of alternate channels in an otherwise silicon MOSFET structure.

### Long term

Synergistic exploration of new materials, structures and information processing architectures.

# **CMOS Devices and Beyond Conclusions**

#### CMOS Devices ...

- MOSFET Scaling Issues

- Low Power MOSFETs WILL need High-K Dielectric in 2005

- High Performance may stay with SiON Gate Dielectric

- Non-Classical CMOS Structures

- Ultra-Thin Body MOSFETs

- Channel Engineered Structures

- FinFETs (Good advancement by several laboratories)

- Double Gate Structures

### ... And Beyond

- Potential of Molecular, Nanowire and Nanotube Electronics

- Near Term MOSFET-like Switches

- Long Term New Information Processing Technology

- Limits on Integration Density Power.

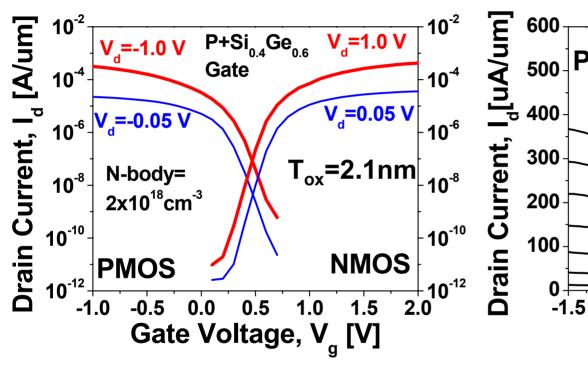

## **FinFET I-V Characteristics**

$L_g=15$ nm,  $W_{fin}=10$ nm